模擬集成電路設(shè)計(jì) 從理論到實(shí)踐的核心指南

模擬集成電路(Analog IC)設(shè)計(jì)是電子工程領(lǐng)域中一門既復(fù)雜又充滿藝術(shù)性的學(xué)科,它專注于處理連續(xù)變化的電壓和電流信號(hào)。與數(shù)字集成電路處理離散的“0”和“1”不同,模擬電路直接與真實(shí)世界(如聲音、光線、溫度、壓力)的連續(xù)信號(hào)交互,因此其設(shè)計(jì)對(duì)噪聲、非線性、功耗和工藝偏差極為敏感。本文旨在為初學(xué)者和有經(jīng)驗(yàn)的設(shè)計(jì)者提供一個(gè)核心指南,涵蓋設(shè)計(jì)流程、關(guān)鍵模塊與最佳實(shí)踐。

一、 設(shè)計(jì)流程概覽

一個(gè)典型的模擬IC設(shè)計(jì)遵循系統(tǒng)化的流程:

- 需求分析與系統(tǒng)規(guī)劃:明確電路規(guī)格,如增益、帶寬、功耗、電源電壓、噪聲系數(shù)、線性度(如IIP3)、工藝節(jié)點(diǎn)等。這些是設(shè)計(jì)成敗的基石。

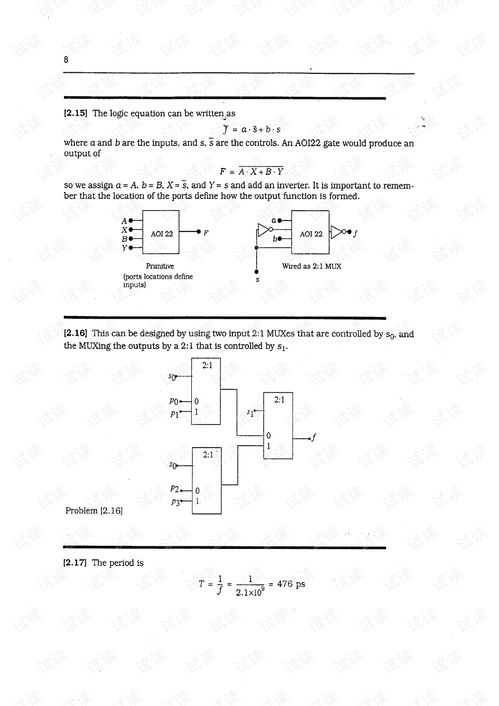

- 架構(gòu)選擇與拓?fù)湓O(shè)計(jì):根據(jù)規(guī)格選擇合適的電路架構(gòu),例如運(yùn)算放大器(Op-Amp)是采用折疊共源共柵、兩級(jí)米勒補(bǔ)償還是軌到軌結(jié)構(gòu)?這需要深入理解各種拓?fù)涞膬?yōu)缺點(diǎn)。

- 晶體管級(jí)設(shè)計(jì):這是設(shè)計(jì)的核心。確定每個(gè)MOSFET或BJT的尺寸(W/L)、偏置點(diǎn),通過手工計(jì)算(如平方律模型、gm/Id方法)結(jié)合EDA工具的仿真來滿足性能指標(biāo)。

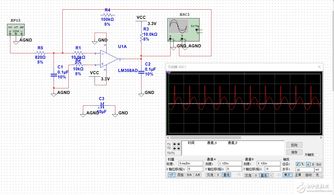

- 仿真與驗(yàn)證:使用SPICE類工具(如Cadence Spectre, HSPICE)進(jìn)行深入的仿真分析,包括:

- 直流(DC)分析:確定工作點(diǎn)。

- 交流(AC)分析:評(píng)估頻率響應(yīng)、增益和相位裕度(穩(wěn)定性)。

- 瞬態(tài)(Transient)分析:觀察時(shí)域響應(yīng)和大信號(hào)行為。

- 噪聲(Noise)分析:量化電路引入的噪聲。

- 工藝角(Corner)與蒙特卡洛(Monte Carlo)分析:評(píng)估制造工藝波動(dòng)和器件失配對(duì)性能的影響,確保設(shè)計(jì)的魯棒性。

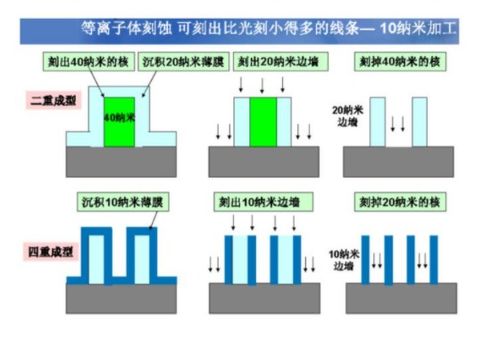

- 版圖設(shè)計(jì):將電路圖轉(zhuǎn)化為物理掩模圖形。模擬版圖是藝術(shù)與科學(xué)的結(jié)合,必須精心處理匹配、噪聲隔離(保護(hù)環(huán))、寄生效應(yīng)、電流密度和天線效應(yīng)等問題。

- 后仿真:提取版圖的寄生電阻電容(RC Extraction)后,再次進(jìn)行仿真,驗(yàn)證物理實(shí)現(xiàn)是否仍滿足所有規(guī)格。

- 流片與測(cè)試:將設(shè)計(jì)數(shù)據(jù)(GDSII)送至晶圓廠制造,芯片返回后進(jìn)行實(shí)際測(cè)試,與仿真結(jié)果對(duì)比。

二、 關(guān)鍵模塊與設(shè)計(jì)要點(diǎn)

- 運(yùn)算放大器(Op-Amp):模擬設(shè)計(jì)的“工作馬”。核心指標(biāo)包括開環(huán)增益、單位增益帶寬(GBW)、相位裕度、壓擺率、輸入/輸出擺幅、共模抑制比(CMRR)和電源抑制比(PSRR)。設(shè)計(jì)時(shí)常在增益、帶寬、功耗和面積之間進(jìn)行折衷。

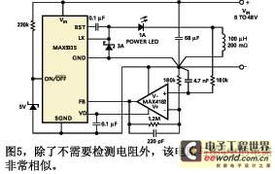

- 偏置電路:為整個(gè)芯片提供穩(wěn)定、與工藝和溫度變化無關(guān)的參考電流/電壓。帶隙基準(zhǔn)(Bandgap Reference)是最核心的模塊之一。

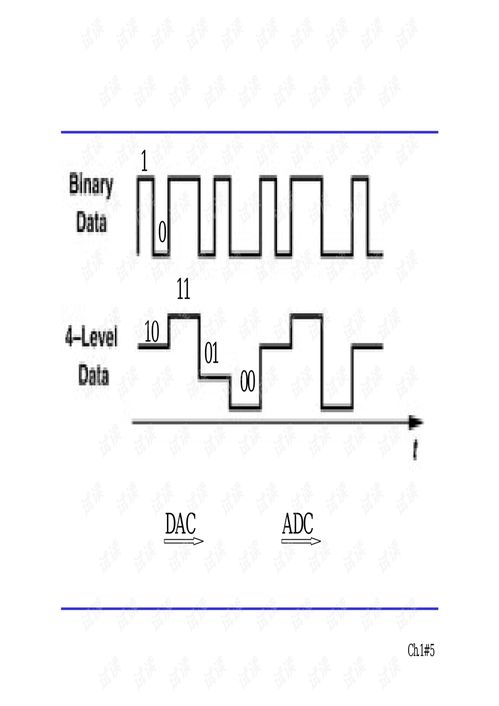

- 數(shù)據(jù)轉(zhuǎn)換器:連接模擬與數(shù)字世界的橋梁。

- 模數(shù)轉(zhuǎn)換器(ADC):如逐次逼近型(SAR)、流水線型(Pipeline)、Σ-Δ型,各有其速度、精度和功耗的權(quán)衡。

- 數(shù)模轉(zhuǎn)換器(DAC):如電流舵型、電阻/電容陣列型。

- 鎖相環(huán)(PLL)與時(shí)鐘電路:用于頻率合成和時(shí)鐘恢復(fù),包含鑒相器、電荷泵、環(huán)路濾波器和壓控振蕩器(VCO)等關(guān)鍵子模塊。相位噪聲和抖動(dòng)是關(guān)鍵指標(biāo)。

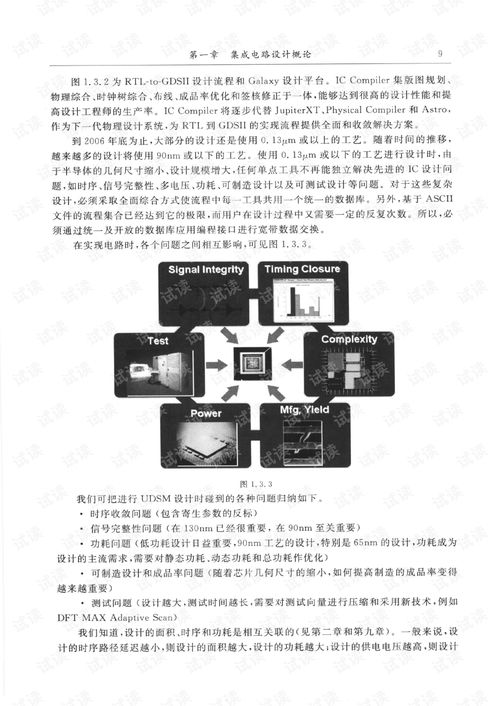

三、 核心挑戰(zhàn)與設(shè)計(jì)哲學(xué)

- 噪聲管理:熱噪聲、閃爍噪聲(1/f噪聲)是模擬電路的天敵。設(shè)計(jì)中需通過增大器件尺寸、采用共源共柵結(jié)構(gòu)、合理濾波等方式抑制噪聲。

- 匹配性:差分對(duì)、電流鏡等對(duì)器件匹配要求極高。版圖上必須采用共質(zhì)心、交叉耦合等布局技術(shù),并注意環(huán)境梯度(如溫度、應(yīng)力)的一致性。

- 電源與襯底噪聲隔離:在混合信號(hào)芯片中,數(shù)字開關(guān)噪聲會(huì)通過電源線和襯底耦合到敏感的模擬部分。設(shè)計(jì)中必須使用獨(dú)立的電源軌、深N阱隔離、保護(hù)環(huán)和片上去耦電容。

- 仿真與現(xiàn)實(shí)的鴻溝:SPICE模型并非完美,尤其是納米級(jí)工藝下,二階、三階效應(yīng)顯著。設(shè)計(jì)者必須理解模型局限,預(yù)留足夠的設(shè)計(jì)余量(Margin)。

四、 工具與技能

現(xiàn)代模擬IC設(shè)計(jì)高度依賴EDA工具鏈(如Cadence, Synopsys, Mentor Graphics),但工具的熟練使用不能替代扎實(shí)的半導(dǎo)體物理、器件模型和電路理論功底。一名優(yōu)秀的模擬設(shè)計(jì)師既是科學(xué)家,也是工程師,需要具備直覺、耐心和解決問題的創(chuàng)造力。

###

模擬集成電路設(shè)計(jì)是一條充滿挑戰(zhàn)但回報(bào)豐厚的道路。它要求設(shè)計(jì)者對(duì)電子學(xué)的基本原理有深刻的理解,并具備在復(fù)雜約束下進(jìn)行優(yōu)化和折衷的能力。隨著工藝節(jié)點(diǎn)的不斷演進(jìn)和系統(tǒng)集成度的提高,模擬設(shè)計(jì)的角色非但沒有減弱,反而變得更加關(guān)鍵。持續(xù)學(xué)習(xí)、動(dòng)手實(shí)踐并從每一次流片(無論成功與否)中汲取經(jīng)驗(yàn),是通往精通的唯一途徑。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.savecan.com.cn/product/98.html

更新時(shí)間:2026-04-27 20:44:15